Waveform Analysis Language

A programming language for complex waveform analysis and EDA tool development

Features

(in-groups '("top.in_" "top.out_") (print CG ":") (whenever (&& clk (! reset) #ready #valid) (print INDEX ":" #data)))

Natural Expression of Hardware Problems

WAL knows what matters in the hardware domain. With WAL it is possible to access signals, step through the waveform or explore the design hierarchy without hundreds of lines of boilerplate.

>-> SIGNALS (clk reset comp1.ack comp1.req) >-> (find (&& comp1.ack comp1.req)) (15 26 102)

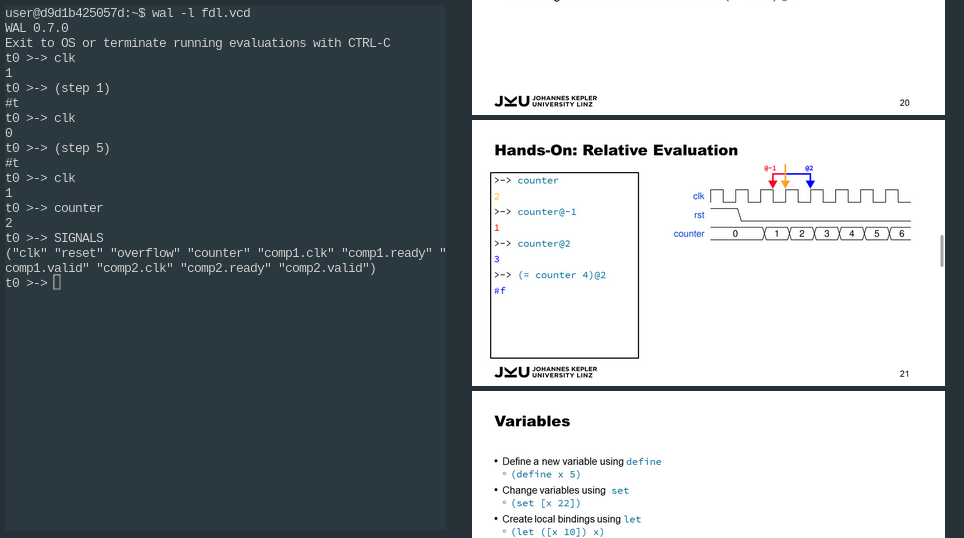

Interactive Development

WAL has a REPL and can be used for interactive debugging, design understanding, and live WAL programming.

wal.load("trace.vcd") bug_locations = wal.eval("(find condition)") for loc in bug_locations: bug = Bug("Unacknowledged", bug_location) db.insert(bug)

Works for you

WAL is a Python package and can be implemented in virtually every workflow. You can use it embedded in Python like SQL or write standalone WAL scripts.

News

👋 SonicRV using WAL @ IEEE Access (January 2026) 🚀

Our open-access journal paper SonicRV: An Educational Platform for Web-Based Simulation and Visualization of RISC-V Processor Architectures has been published in IEEE Access. SonicRV is a web-based educational platform that lets students write RISC-V assembly programs, simulate them on VHDL implementations of single-cycle, multicycle, and pipelined processors, and explore the results through synchronized visualizations.

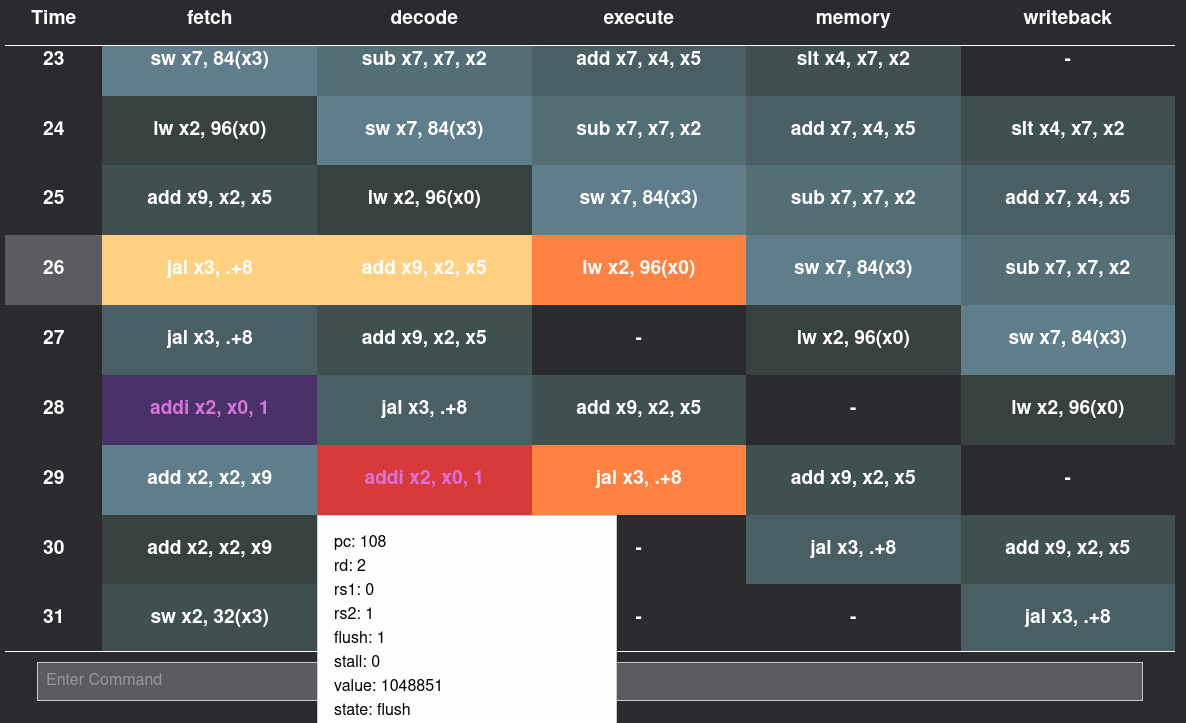

In SonicRV, WAL is used to extract and process information from the simulation waveforms generated when executing a program on the processor. The WAL-based analysis reads the relevant signal values at the correct timestamps and aggregates them for the interactive visualizations, such as the architectural state, block diagrams, state machines, and pipeline diagrams.

You can find the article here.

Link to SonicRV platform is here.

Surfer & WAL @ CAV'25

We presented the paper Surfer — An Extensible Waveform Viewer at this year’s Computer Aided Verification Conference (CAV). Surfer is a modern, open-source waveform viewer designed to integrate with the broader hardware design ecosystem. It supports translation from raw bit vectors to semantically meaningful values, integration with simulation and verification tools, and lays the groundwork for interactive simulation in the open-source ecosystem.

In the paper, WAL is one of the tools integrating Surfer: the WAL runtime uses Surfer to display the results of waveform analysis programs written in WAL. Analysis results can be injected as additional signals into Surfer, allowing users to inspect WAL-computed information directly alongside the original waveform data.

You can find the paper here.

WAL @ FDL'24

We presented the paper An Extensible and Flexible Methodology for Analyzing the Cache Performance of Hardware Designs at this year’s Forum on Specification and Design Languages (FDL). The paper introduces an automated methodology for analyzing cache performance during HDL design by monitoring cache interfaces in waveforms from simulators, formal tools, or logic analyzers.

In the paper, WAL is used as the foundation of the methodology: a generic WAL-based cache analysis algorithm scans waveforms for cache requests, responses, and dropped requests, while reusable WAL metrics compute results such as hit rates, average delays, and visualizations. Only a small amount of design-specific glue code is needed to bind the generic analysis to a concrete cache implementation, making the approach reusable across designs and design configurations.

You can find the paper here.

WAL @ DATE'24

We presented a paper about Formal SYNthesis (FSYN) at this year’s Design, Automation and Test in Europe Conference (DATE). FSYN optimizes circuit netlists under external constraints by removing gates that are redundant under these constraints.

In the paper, WAL is used in FSYN’s rule filtering phase: after valid stimuli are generated and simulated, WAL analyzes the resulting waveforms for every gate and optimization rule to quickly find counterexamples that refute rules before expensive formal checks are launched. This reduces the number of required formal proofs and can significantly speed up the overall optimization flow.

You can find the paper here.

👋 TCAD Journal: WAL Article accepted 🌊

Recently, the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD) Journal accepted a new article about WAL. It is called "WAVING Goodbye to Manual Waveform Analysis in HDL Design With WAL" and provides an extended introduction to WAL including many new features such as the macro system and new experiments.

Most importantly, the paper is open-access, that means anybody can read it for free.

You can find the early access version of the article here.

안녕하세요 (hello) from ASP-DAC'24

We will present a paper about WAL at this year's ASP-DAC in Incheon, Korea. In this paper, we introduced Virtual Signals to WAL. Virtual Signals allow you to inject new Signals into already existing waveforms. Even better, these Signals are not limited to only holding n-bit values but every WAL value, even hash maps.

You can find the paper here.

WAL Tutorial at FDL'23 and a new Publication

We held a tutorial about WAL at this years Forum on specification & Design Languages (FDL) in beatiful Turin, Italy! Participants could easily try WAL via a webpage which teleported them directly into a WAL environment.

The slides of the tutorial are available here, so you can now do the tutorial from the comfort of your own shell!

In addition, we also had a paper accepted at FDL. This paper is a collaboration with the developers of Spade HDL from Linköping University. In this paper we integrated Spade and WAL, and now people that use Spade IP can automatically enjoy waveform analysis without lifting a finger. You can find the paper here.

First RISC-V Summit Europe

In June, we went to the first RISC-V Summit Europe in Barcelona. It was a great event, with many interesting talks, posters, and lots of discussions with folks from all parts of the RISC-V ecosystem.

We presented our WAL-based pipeline explorer, which allows you to easily see what's going on in processor pipelines.

WAL @ DVCON Europe'22

WAL 0.6.3 beta released

WAL @ DAC'22