Waveform Analysis Language

A programming language for complex waveform analysis and EDA tool development

Features

(in-groups '("top.in_" "top.out_") (print CG ":") (whenever (&& clk (! reset) #ready #valid) (print INDEX ":" #data)))

Natural Expression of Hardware Problems

WAL knows what matters in the hardware domain. With WAL it is possible to access signals, step through the waveform or explore the design hierarchy without hundreds of lines of boilerplate.

>-> SIGNALS (clk reset comp1.ack comp1.req) >-> (find (&& comp1.ack comp1.req)) (15 26 102)

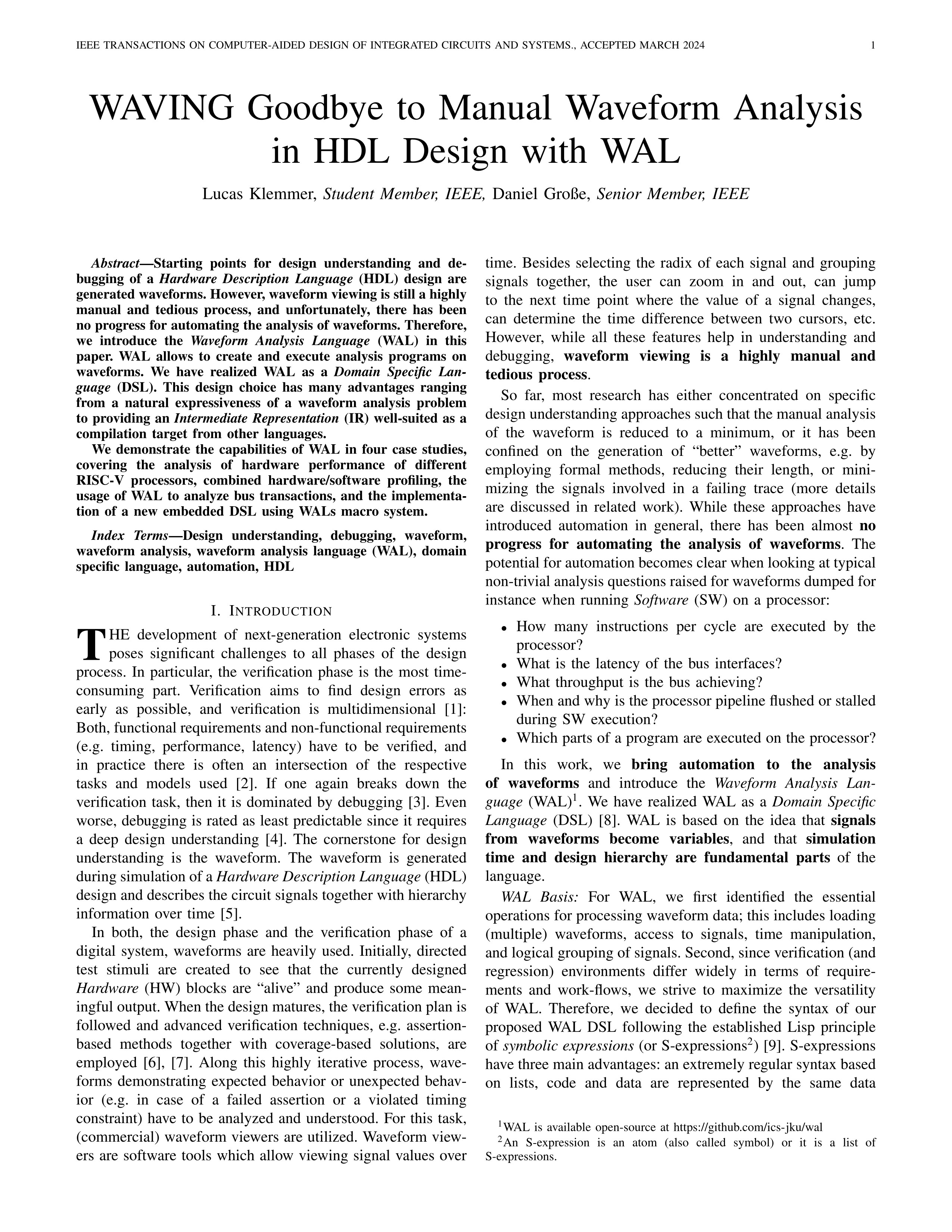

Interactive Development

WAL has a REPL and can be used for interactive debugging, design understanding, and live WAL programming.

wal.load("trace.vcd") bug_locations = wal.eval("(find condition)") for loc in bug_locations: bug = Bug("Unacknowledged", bug_location) db.insert(bug)

Works for you

WAL is a Python package and can be implemented in virtually every workflow. You can use it embedded in Python like SQL or write standalone WAL scripts.

News

👋 TCAD Journal: WAL Article accepted 🌊

Recently, the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD) Journal accepted a new article about WAL. It is called "WAVING Goodbye to Manual Waveform Analysis in HDL Design With WAL" and provides an extended introduction to WAL including many new features such as the macro system and new experiments.

Most importantly, the paper is open-access, that means anybody can read it for free.

You can find the early access version of the article here.

안녕하세요 (hello) from ASP-DAC'24

We will present a paper about WAL at this year's ASP-DAC in Incheon, Korea. In this paper, we introduced Virtual Signals to WAL. Virtual Signals allow you to inject new Signals into already existing waveforms. Even better, these Signals are not limited to only holding n-bit values but every WAL value, even hash maps.

You can find the paper here.

WAL Tutorial at FDL'23 and a new Publication

We held a tutorial about WAL at this years Forum on specification & Design Languages (FDL) in beatiful Turin, Italy! Participants could easily try WAL via a webpage which teleported them directly into a WAL environment.

The slides of the tutorial are available here, so you can now do the tutorial from the comfort of your own shell!

In addition, we also had a paper accepted at FDL. This paper is a collaboration with the developers of Spade HDL from Linköping University. In this paper we integrated Spade and WAL, and now people that use Spade IP can automatically enjoy waveform analysis without lifting a finger. You can find the paper here.

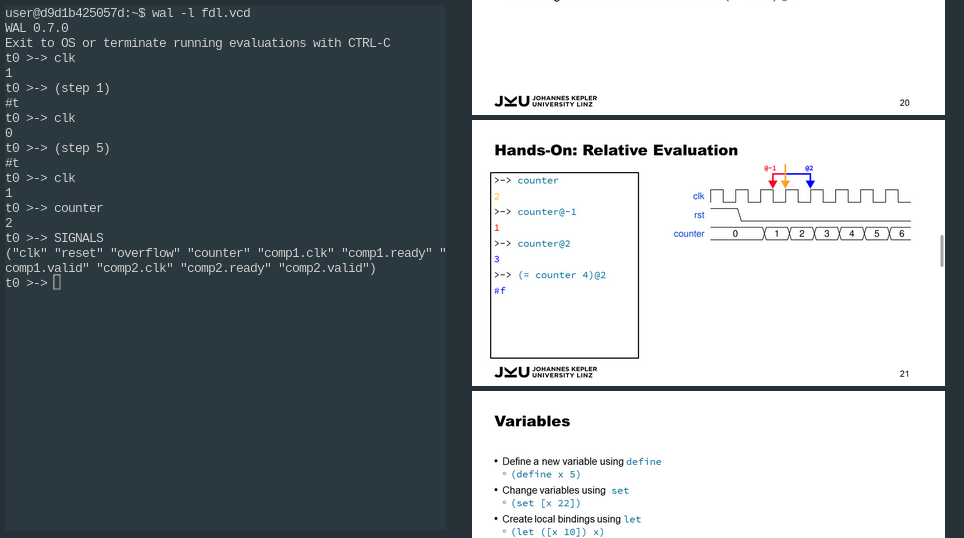

First RISC-V Summit Europe

In June, we went to the first RISC-V Summit Europe in Barcelona. It was a great event, with many interesting talks, posters, and lots of discussions with folks from all parts of the RISC-V ecosystem.

We presented our WAL-based pipeline explorer, which allows you to easily see what's going on in processor pipelines.

WAL @ DVCON Europe'22

WAL 0.6.3 beta released

WAL @ DAC'22